## Through Silicon Via Technology: The Ultimate Market for 3D Interconnect

Publication date: January 2008

Through-hole silicon via (TSV) is the ultimate 3D interconnect. The industry is moving past the feasibility (R&D) phase for TSV technology into the commercialization phase where economic realities will determine which technologies are adopted. Low-cost fine via hole formation and highly reliable via filling technologies have been demonstrated; process equipment and materials are available. Even though design, thermal, and test issues remain, much progress has been made. Is 3D interconnect with TSV the answer to the interconnect crisis? Which technologies will be adopted? Will vias be formed during the wafer fabrication process or during IC packaging and assembly? What are the limitation factors to the adoption of this new technology? This report provides answers to these questions.

This TechSearch International report highlights the major processes and materials used by each company, including via fabrication methods, via filling, wafer thinning, and bonding methods. The report provides an update on activities of research organizations and key technologies used. A carefully developed forecast for market size in number of wafers is provided for each application area. Applications for 3D TSV include image sensors, flash, DRAM, processors, FPGAs, and power amplifiers. The timing for mass production depends on how the TSV compares in terms of cost with existing technologies. A timeline for the adoption of these applications is provided. Full text analysis provides critical details of the new developments and applications with photos and graphs of market projections.

Drivers, Markets, and Technical Issues

**Executive Summary**

- 1 3D TSV Interconnect Drivers

- 1.1 Historical 3D Packaging

- 1.2 Wafer Level 3D Integration with TSV

- 1.3 Silicon Carrier Packaging with TSV

- 1.4 Addressing Interconnect Delay

- 1.5 Memory Latency

- 1.6 Power

- 1.7 Noise

- 2 Significant Technical Developments

- 2.1 Foundry Vias

- 2.1.1 Vias First versus Vias Last

- 2.2 Laser Processing TSV

- 2.3 Via Fill

- 2.4 IMP Sputtering for Via Filling

- 2.5 Bonding to Handle Wafers

- 2.6 Integration of Passives

- 3 Corporate Developments ASE, ALLVIA, Amkor, Chartered Semiconductor, Cubic Wafer, Elpida Memory, Inc., Freescale, Fujikura, Infineon, Intel, Jazz Semiconductor, Micron, NEC, NXP, Oki Electric, Renesas, Samsung, Sanyo, Schott Glass, Sharp,

Silex Microsystems, STATSChipPAC, STMicroelectronics, Tessera, Texas Instruments, Tezzaron, Toshiba, TSMC, UTAC, Ziptronix, ZyCube

- 4 Research Organizations and Universities ASET, CEA-LETI, EMC-3D Consortium, e-Cubes Project, Fraunhofer IZM Munich, IME, IMEC, ITRI, Lincoln Labs, MIT, Rensselaer Polytechinc Institute, Research Triangle Institute, Sematech, Tohoku University, University of Arkansas

- 5 Market Forecast

- 5.1 Chip-on-Chip

- 5.2 Image Sensors

- 5.3 Power Amplifier Devices

- 5.4 DRAM

- 5.5 Processors

- 5.6 Field Programmable Gate Arrays

- 5.7 Flash Memory

- 5.8 Power Devices

- 6 Technical Issues and Barriers to Growth 6.1 Design Issues

4801 Spicewood Springs Road • Suite 150 Austin, Texas 78759 Tel: 512-372-8887 • Fax: 512-372-8889 tsi@techsearchinc.com • www.techsearchinc.com

## Through Silicon Via Technology: The Ultimate Market for 3D Interconnect

- 6.2 What is Different in 3D Design?

- 6.3 3D CAD

- 6.3.1 Adapting 2D Tools for 3D Use

- 6.3.2 Customized 3D Tools

- 6.3.3 True 3D University Tools

- 6.4 Thermal Issues

- 6.5 Test Issues

Partial List of Figures and Tables

- TSV market projection in number of devices

- TSV market projection in number of wafers

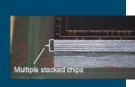

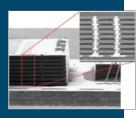

- Various stacked die and stacked package configurations

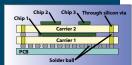

- Silicon substrate with TSV for multichip SOP applications

- Repartitioning the Intel Core 2 Processor

- Examples of via-first technology

- Front-to-front, vias last, without carrier wafer

- FEOL or BEOL vias first with handle wafer

- Vias from the backside after bonding

- Laser vias in silicon (10 x 70 μm)

- Design partitioning for 3D interconnect

- Cubic Wafer process flow

- Via first process for DRAM

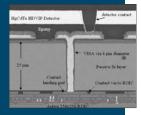

- Cross section of Freescale/LETI 3D structure

- Fujikura's TSV interposer

- Infineon's SOLID face-to-face bonding technology

- Intel's TSV cross-section

- Conventional 4GB DRAM versus Stacked DRAM with TSV

- Cu/Sn eutectic microbump bonding

- Stacked DRAM process flow

- DRAM stacked package process

- Renesas TSV formation process

- Renesas bonding technology

- Renesas 10 chip stack

- Samsung NAND flash with TSV

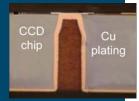

- Sanyo image processor with TSVs

- Tessera's CMOS image sensor using backside via

Fax to 512-372-8889 or Email to tsi@techsearchinc.com

- Tezzaron FaStack  $\ensuremath{^{\rm Tezzaron}}$  technology for memory devices

- Toshiba's image sensor with TSV

- DBI process flow

- Ziptronix 10µm pitch DBI bond

- ZyCSP™ TSV filled with conductive paste

- ICV-SLID process

- IMEC's temporary bonding for 3D die thinning

- IMEC's thinning and stacking process

- RPI vias-last process

- RPI via first approach

- Vertically interconnected VISA device cross-section

- 3D applications and required via diameter

- Drivers for DRAM TSV

- Proposed FPGA 3D versus 2D delay

- Cost of TSV versus next silicon technology node

- · Module level partitioning of two-core OpenRisc processor

- Temperature profile of one chip within a 3D stack

- Cadence Virtuosa customized via external scripts

- Thermal profile with thermal via placement

- Potential Drivers for 3D Integration

- 3D TSV Announcements

- Impact of Partitioning on Latency for Intel's Processor

- Via Etch and Fill Methods

- Insulator and Metallization Selections

- Bonding Choices

- 3D Process Flows

- Process Sequences for 3D Integration

- Ziptronix DBI interconnect reliability data.

- Shipments of Image Sensors with TSVs

- Shipments of Power Amplifier Devices with TSVs

- Shipments of DRAM with TSVs

- Shipments of Processors with TSVs

- Shipments of FPGAs with TSVs

- Shipments of NAND Flash with TSVs

- Different Styles of 3D Design

## Main Differences Between 2D and 3D Design

| Name:                       |         |            | Email:                                    |                                     |  |

|-----------------------------|---------|------------|-------------------------------------------|-------------------------------------|--|

| Position:                   |         |            | Telephone:                                |                                     |  |

| Company:                    |         |            | Fax:                                      |                                     |  |

| Ship to Address:            |         |            | Bill to Address:                          | Bill to Address:                    |  |

|                             |         |            |                                           |                                     |  |

| Purchase Order Number:      |         |            |                                           |                                     |  |

| AMEX, Visa, MC, JCB:        |         |            | Exp. Dat                                  | e:                                  |  |

| Report Price:               | \$      | \$4,000.00 |                                           |                                     |  |

| Additional Copies (\$500 ea | ch): \$ |            |                                           |                                     |  |

| Shipping & Handling:        | \$      |            | (\$25 pdf, \$30 Domestic-UPS 2nd day; \$3 | 5 International-US Global Priority) |  |

| Total Amount:               | \$      |            |                                           |                                     |  |